# Lab2 Scan Chain Insertion and ATPG Using Tessent

Prof: Chia-Tso Chao

TA: Ting-Wei Chen

2024-12-09

## Outline

- Introduction

- □ Tessent Scan

- □ Tessent Fastscan

- Mixed Flow

- □ Lab

## Outline

- Introduction

- Tessent Scan

- Tessent Fastscan

- ☐ Mixed Flow

- **L**ab

#### Introduction

- □ This lab focuses on ATPG with tools from 2 different EDA vendors

- Synopsys

- Mentor Graphics

- □ Tessent Scan inserts scan chains

- Basically replaces FFs with scan-FFs

- □ Tessent Fastscan performs ATPG and fault simulation

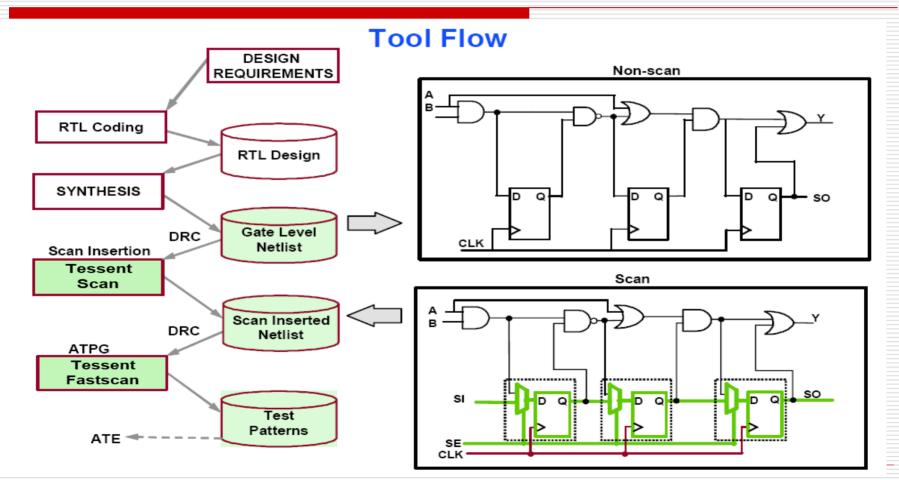

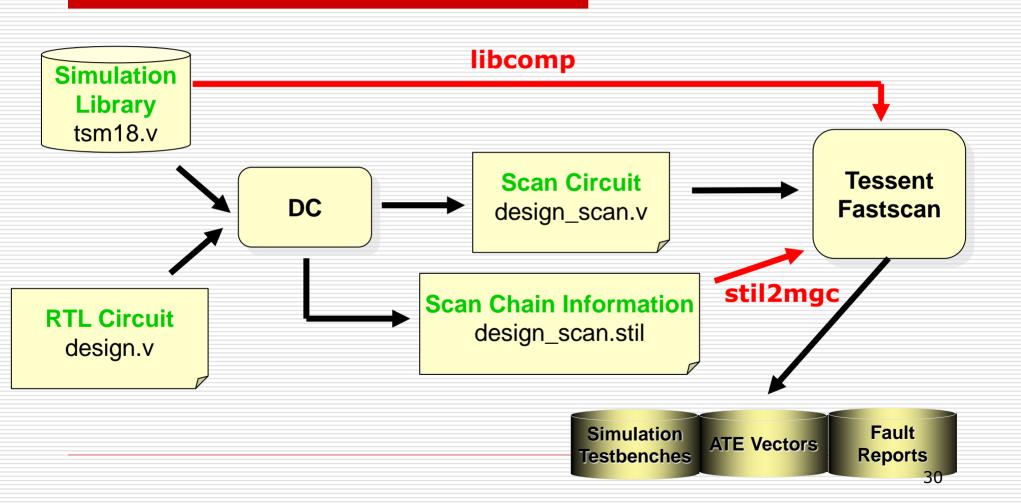

## Insert Scan and ATPG Flow

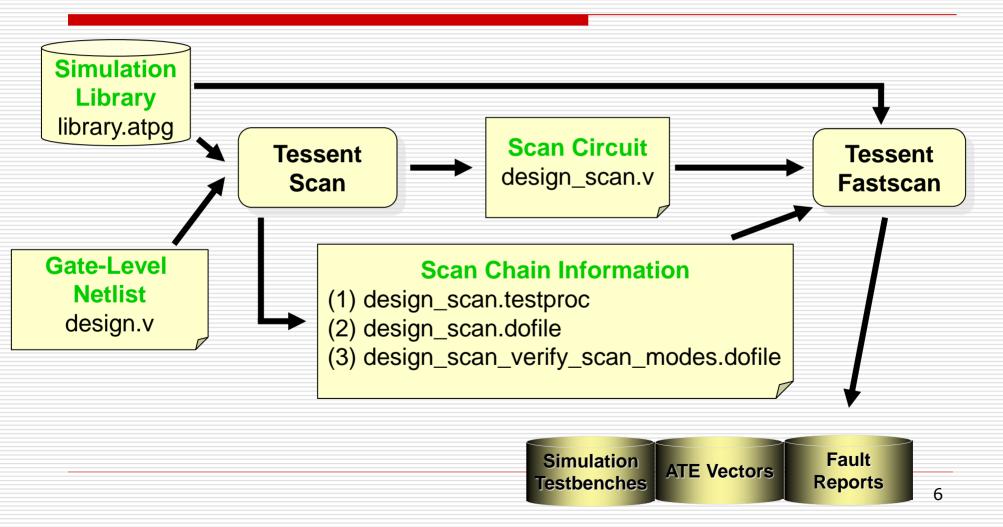

## Input/Output Files

## Outline

- □ Tessent Scan

- ☐ Tessent Fastscan

- Mixed Flow

#### Invoke Tessent Scan

- □ Invoke Tessent shell

- \$ tessent -shell

- □ Default system mode is "SETUP"

- You'll see the prompt shows

- SETUP>

- ☐ Set context to "dft -scan"

- Which corresponds to Tessent Scan

- SETUP> set\_context dft -scan

## Read Verilog and Library File

- ☐ Load cell library into the tool

- Library is in Mentor Graphics' own format

- SETUP> read\_cell\_library l90sprvt.atpg

- ☐ Read in Verilog source file

- An already-synthesized gate-level netlist

- SETUP> read\_verilog pre\_norm\_noscan.v

# Specify Top Module and Clock

- □ Specify the top level of the design

- SETUP> set\_current\_design pre\_norm

- Clocks are primary input signals that synchronously change the state of sequential logic elements

- SETUP> add clocks 0 clk ← primary input to design

- positive edge-triggered signal

- Check the clock list

- SETUP> report\_clocks

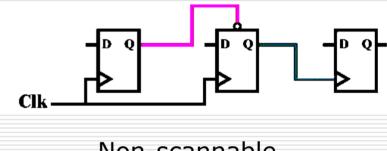

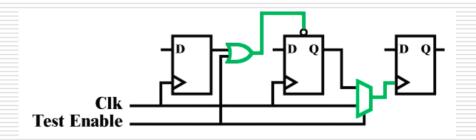

# Setup Test Logic Configuration

- □ Test logic options make clock lines controllable to get a scannable design

- SETUP> set\_test\_logic -clock on -reset on

Non-scannable

- Verify test logic configuration with

- report\_environment

Scannable after test logic insertion

## Entering Analysis System Mode

- □ Enter netlist analysis mode and perform scan identification

- SETUP> set\_system\_mode analysis

## Insert Scan Chain and View Report

- Specify number of scan chains

- ANALYSIS> set\_scan\_insertion\_options -chain\_count 10

- Distributes scan cells over new scan chains

- ANALYSIS> analyze\_scan\_chains

- □ Insert scan chain and add test logic circuitry

- ANALYSIS> insert\_test\_logic

- □ Report all defined scan chains & test logic

- INSERTION > report\_scan\_chains

- INSERTION> report\_test\_logic

# Output Scan Design for ATPG

- Write out scan design and setup files

- INSERTION> write\_design -output pre\_norm\_scan.v -replace

- INSERTION> write\_atpg\_setup pre\_norm\_scan -replace | <design>

```

<design>.testproc: test procedure file

<design>.dofile: setup information for ATPG

<design>_verify_scan_modes.dofile: TOP setup script for ATPG

```

## Outline

- ☐ Tessent Scan

- □ Tessent Fastscan

- Mixed Flow

- Lab

#### Invoke Tessent Fastscan and ATPG Setup

- Change system mode to setup

- INSERTION> set\_system\_mode setup

- Setup ATPG and switch to Tessent Fastscan

- SETUP> dofile pre\_norm\_scan\_verify\_scan\_modes.dofile

- Select fault type: stuck-at, IDDQ, transition, path delay, bridge, etc.

- ANALYSIS> set\_fault\_type stuck

## Generate Patterns (1/2)

- ☐ Use "-auto" option to

- Suggest the best settings possible to

- Generate the most compact patterns

- With the highest coverage

- Within the lowest time

- ANALYSIS> create\_patterns -auto

## Generate Patterns (2/2)

Without the "auto" option, you can specify your own configurations using these commands

```

ANALYSIS> set_atpg_limits

-cpu_seconds [integer]

-test_coverage [real]

-pattern_count [integer]

ANALYSIS> set_abort_limit [integer]

ANALYSIS> create patterns

```

# During ATPG Run

#### □ ATPG is performed one pass after another

| Simulation performed for #gates = 3420 #faults = 5542<br>system mode = ATPG pattern source = internal patterns |          |         |          |                 |     |                     |           |  |  |  |

|----------------------------------------------------------------------------------------------------------------|----------|---------|----------|-----------------|-----|---------------------|-----------|--|--|--|

| simulated                                                                                                      | coverage | in list | detected | # eff. patterns |     | process<br>CPU time | RE/AU/AAB |  |  |  |

|                                                                                                                |          |         |          |                 |     | 1.15 sec            | 0/0/15    |  |  |  |

| 64                                                                                                             | 87.16%   | 781     | 4761     | 60              | 60  | 1.23 sec            | , ,       |  |  |  |

|                                                                                                                |          |         |          |                 |     | 2.33 sec            | 87/1/91   |  |  |  |

| 128                                                                                                            | 95.93%   | 243     | 450      | 51              | 111 | 2.33 sec            |           |  |  |  |

|                                                                                                                |          |         |          |                 |     | 2.58 sec            | 117/1/103 |  |  |  |

| 192                                                                                                            | 98.81%   | 70      | 143      | 50              | 161 | 2.59 sec            |           |  |  |  |

|                                                                                                                |          |         |          |                 |     | 2.59 sec            | 117/1/103 |  |  |  |

| 229                                                                                                            | 99.73%   | 15      | 55       | 31              | 192 | 2.59 sec            |           |  |  |  |

#### ATPG Result

- 4 main parts

- Fault number (#FU)

- Test/Fault coverage

- Pattern count

- Runtime

- Print ATPG statistics report

- ANALYSIS> report\_statistics

| Statistics Report<br>Stuck-at Faults                                                                     |                                                                                           |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Fault Classes                                                                                            | #faults<br>(total)                                                                        |  |  |  |  |  |  |

| FU (full)                                                                                                | 6098                                                                                      |  |  |  |  |  |  |

| UO (unobserved) DS (det_simulation) DI (det_implication) UU (unused) RE (redundant) AU (atpg_untestable) | 15 ( 0.25%)<br>5409 (88.70%)<br>540 ( 8.86%)<br>16 ( 0.26%)<br>117 ( 1.92%)<br>1 ( 0.02%) |  |  |  |  |  |  |

| Coverage                                                                                                 |                                                                                           |  |  |  |  |  |  |

| <pre>test_coverage fault_coverage atpg_effectiveness</pre>                                               | 99.73%<br>97.56%<br>99.75%                                                                |  |  |  |  |  |  |

| <pre>#test_patterns #simulated_patterns CPU_time (secs)</pre>                                            | 192<br>229<br><mark>300.5</mark>                                                          |  |  |  |  |  |  |

## View Fault Report

- Display fault information

- ANALYSIS> report\_faults -all

- A fault is determined by (i) a fault value and (ii) a fault site

- Each fault is associated with a fault class/code

ATPG> REPort FAults -class ATPG UNTESTABLE Fault value: Either 0 (for stuck-at-0) AU /I\$7/OUT or 1 (for stuck-at-1) EO /I\$7/IN EQ /I\$1/en /IS7/OUT 0 EQ /I\$7/IN Fault code EQ /I\$1/en AU /I\$4/i1 AU /I\$20/en AU \_/I\$20/en Fault site | 0 AU /I\$2/en AU /I\$2/en

# Fault Classes - Full (FU)

- ☐ FU = TE + UT

- ☐ TE: Testable

- □ UT: Untestable

- Faults which no pattern can exist to either detect or possible-detect

- Cannot cause functional failure, so they are excluded from test coverage calculation

# Fault Classes - Testable (TE)

- DT: Detected

- UD: Undetected

- Faults that cannot be proven untestable or ATPG\_untestable

- Initial class for testable faults

- AU: ATPG\_untestable

- Due to pin constraint or insufficient sequential depth placed on Fastscan

- PD: Possible-detected

- Faults with good-machine value being 0 or 1, and faulty machine value being X in simulation

## Fault Classes - Untestable (UT)

- UU: Unused

- Faults not connected to any circuit observation point

- □ BL: Blocked

- Faults whose paths all blocked by tied logic

- ☐ TI: Tied

- Point of the fault value is always same (e.g. SA 0 at AND2 with complementary inputs)

- □ RE: Redundant

- Faults undetectable after exhausting all patterns and need dedicated analysis to verify redundancy

- ANALYSIS> identify\_redundant\_faults

## Test Coverage Formula Comparison

TetraMAX possible detected test\_coverage =  $\frac{DT + (PT * posdet\_credit)}{all faults - (UD + AU * au\_credit)}$  default 0

Tessent Fastscan

$$test\_coverage = \frac{DT + (PD*posdet\_credit)}{testable}*100$$

$$fault\_coverage = \frac{DT + (PD*posdet\_credit)}{full}*100$$

$$ATPG\_effectiveness = \frac{DT + UT + AU + PU + (PT * posdet\_credit)}{full} *100$$

#### Save Patterns

- Save patterns that are generated via ATPG

- Various formats including binwgl, ctl2005, stil2005, stil999, Verilog, VHDL, wgl, zycad, tstl2, utic

- ANALYSIS> write\_patterns pre\_norm\_scan.pat -verilog -proc -replace

- ANALYSIS> write\_patterns pre\_norm\_scan\_tstl2.pat-TSTL2 -replace

- ANALYSIS> exit

Toshiba Standard Tester Interface Language 2

## Outline

- Tessent Scan

- □Tessent Fastscan

- ■Mixed Flow

- □Lab

#### Mixed Flow

- Synopsys Design Compiler is way better at mapping design from RTL code to gatelevel netlist

- Some practices in industrial project hence adopt

- Design Compiler to synthesize gate-level netlist and do scan chain insertion

- Tessent Fastscan to perform ATPG

## Input/Output Files

### Input Files Required in Mixed Flow

- Library file needs to be converted

- From .v to .atpg

- The detailed information as to <u>scan</u> <u>chain</u> needs to be converted

- From .stil to .dofile and .proc

- Scan design

- Gate-level netlist with scan chain inserted

#### Convert STIL File

- Use "stil2mgc" to convert STIL file from Design Compiler into Tessent-compatible dofile and test procedure file

- \$ stil2mgc pre\_norm\_scan.stil

- It generates both files for setup in Fastscan

- pre\_norm\_scan.stil.do

- pre\_norm\_scan.stil.proc

# Perform ATPG using Tessent

- □ Read scan circuit from Design Compiler to perform ATPG

- \$ tessent -shell

- SETUP> set\_context patterns -scan

- SETUP> read\_cell\_library l90sprvt.atpg

- SETUP> read\_verilog pre\_norm\_scan.v

- SETUP> dofile pre\_norm\_scan.stil.do

- SETUP> set\_system\_mode analysis

- ANALYSIS> set\_fault\_type stuck

- ANALYSIS> create\_patterns -auto

- ANALYSIS> report\_statistics

## Outline

- ☐ Tessent Scan

- Tessent Fastscan

- ☐ Mixed Flow

- □ Lab

## Lab Objective

- Compare the following during ATPG using the DC+TMAX, DC+TS and TS flows

- Total fault number

- Test coverage

- Pattern count

- Run time (s)

- □ Run on circuit "pre\_norm"

- DC+TMAX, DC+TS: "pre\_norm.v" in ~/lab1/

- TS: "pre\_norm\_noscan.v" in ~/lab2/

# Example of Lab Result

| Flow    | #Faults | Test Coverage | #Patterns | Run time |

|---------|---------|---------------|-----------|----------|

| DC+TMAX | 71298   | 100%          | 138       | 0.83s    |

| TS      | 122072  | 100%          | 201       | 0.66s    |

| DC+TS   | 75208   | 100%          | 203       | 0.51s    |

#### References

- Mentor Graphics (Siemens)

- Tessent Scan and ATPG User's Manual, v2019.3

- Synopsys

- TetraMAX ATPG User Guide, J-2014.09-SP1

- TestMAX ATPG User Guide, P-2019.03