最新活動與實驗室動態

Electronic Design Automation Algorithms and Implementation.

探索 EDA 核心演算法與實作技術。

一年一度的尾牙聚餐,感謝大家一年的辛勞。

陽光與沙灘的屏東之旅,凝聚實驗室感情。

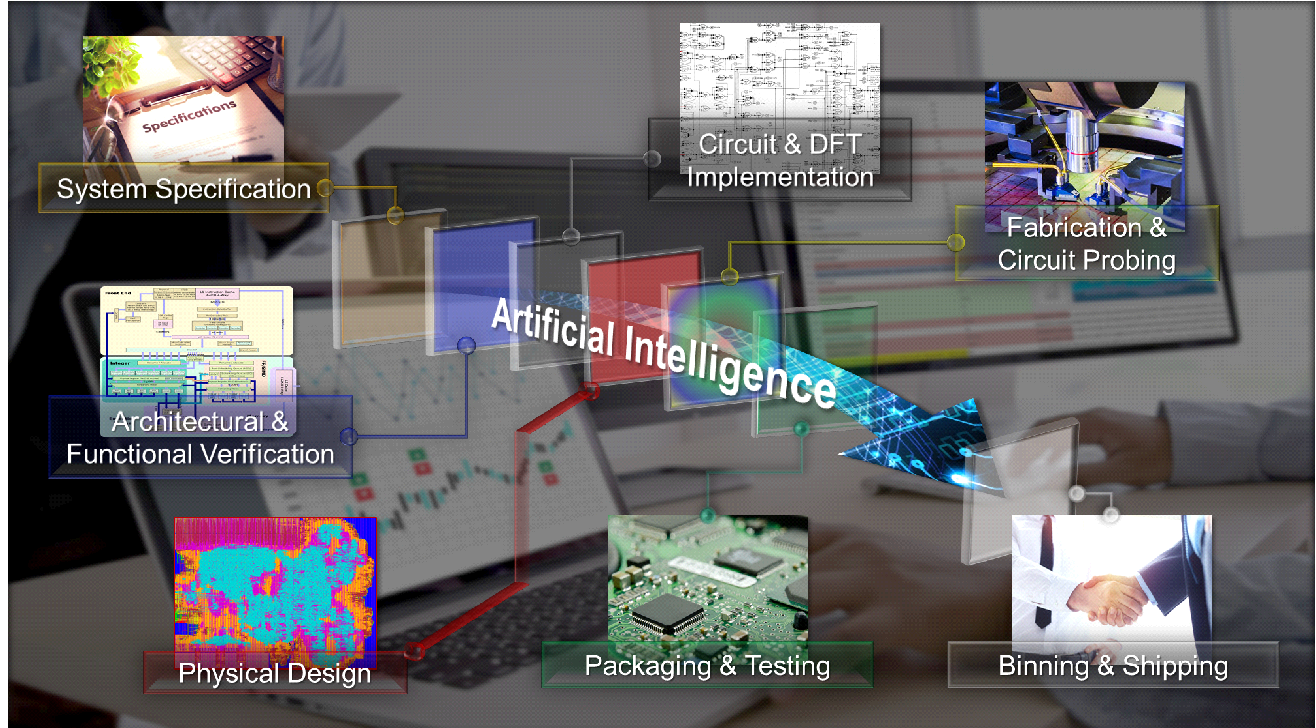

AI Applications & Low DPPM Testing

本實驗室大量使用 深度學習、強化學習 等 AI 技術,來加速產品在開發、製造及測試上的流程,讓產品能更快上市以賺取更多獲利。

已和眾多公司合作過,並應用在像是後端 Power Network 的設計上、WAT 晶圓製造上,以及封裝完後的 Binning 上。此外,我們的技術亦用在產品良率的確保,以創造雙贏的企業與客戶行銷。

我們也將關於 AI 上的應用成果大量發表於知名的國際會議,如 ICCAD、VTS、ISPD、ASPDAC、ITC-Asia 等,而我們近年的成果亦在 ISPD 榮獲 最佳論文 (Best Paper Award)。

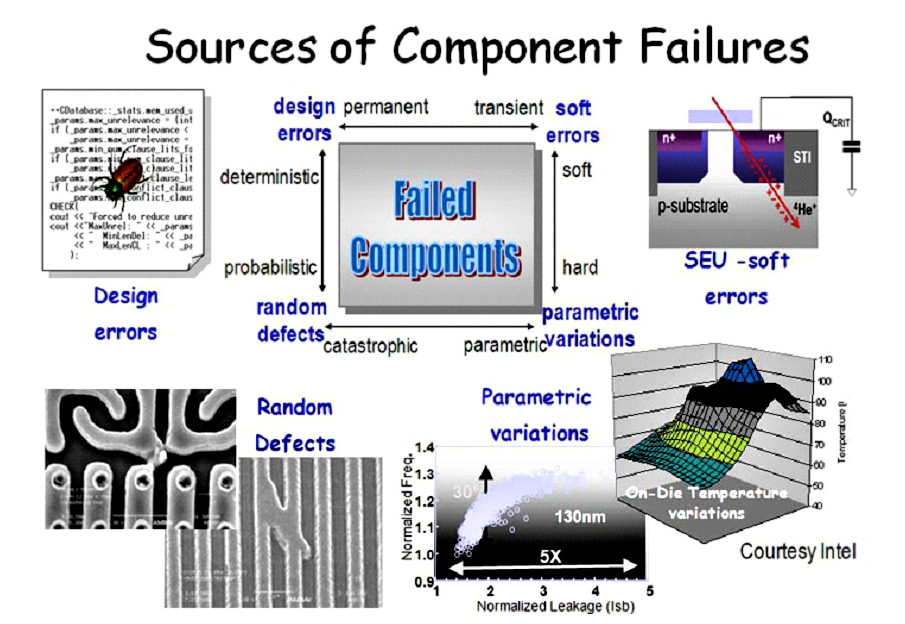

傳統的測試技術中,無論是 stuck-at fault (固定型錯誤)、transition delay fault (轉態延遲錯誤) 等,都只針對標準單元 (standard cell) 外部的連線上的錯誤 (fault) 產生測試向量。然而隨製程日益先進、晶片集成程度越加複雜,許多標準單元內瑕疵導致的錯誤被發現。特別是在對晶片品質要求度高的車用電子,這些細微、傳統測試可能遺漏的瑕疵都不被允許。

因此,近年來 cell-aware test (單元識別測試) 由 Mentor Graphics 所提出。它使用精確的 SPICE 電路模型,模擬當瑕疵存在標準單元時、每筆輸入組合下的錯誤行為。實驗室此領域的研究包含 defect-extraction、defect-injection 與新型態 fault model,都未見於現今的商用測試方案中。

我們的其中一項研究,兩標準單元間發生短路瑕疵 (short defect) 的錯誤模型之產生,也榮獲 2017 VTS 的最佳論文獎。此外,我們的錯誤模型能與商用 ATPG tool 結合產生測試向量並融入實務測試流程中、能給公司帶來立即幫助。我們的方案還獲得瑞昱半導體與聯詠科技採用。

Sources of Component Failures

Distinguished Professor, Dept. of Electronics Engineering, NYCU

Current Master Students

最新精選論文 (2023-2024)

Liang-Ting Chen, Hung-Ru Kuo, Yih-Lang Li, and Mango C.-T. Chao

ACM/IEEE Design Automation Conference (DAC)

Cheng-Che Lu, Chi-Chih Chang... and Mango Chia-Tso Chao

IEEE VLSI Test Symposium (VTS)

Chin-Kuan Lin... and Mango Chia-Tso Chao

VLSI Test Symposium (VTS)

Chia-Heng Yen... and Mango Chia-Tso Chao

IEEE TCAD (Regular Paper)

本實驗室與業界保持緊密合作關係

想加入 VLSI Testing Lab 嗎?這裡有你最想知道的答案。